在通信工程領(lǐng)域,數(shù)據(jù)采集系統(tǒng)是信息獲取、傳輸與處理的基礎(chǔ)環(huán)節(jié),其性能直接影響整個(gè)通信系統(tǒng)的效率與可靠性。隨著5G、物聯(lián)網(wǎng)、工業(yè)互聯(lián)網(wǎng)等技術(shù)的飛速發(fā)展,對(duì)數(shù)據(jù)采集系統(tǒng)的速度、精度、集成度和可靠性提出了前所未有的高要求。因此,設(shè)計(jì)一種高速化與集成化的數(shù)據(jù)采集系統(tǒng),已成為現(xiàn)代通信工程中的一項(xiàng)關(guān)鍵技術(shù)挑戰(zhàn)。

本文旨在探討一種面向通信工程應(yīng)用的高速化與集成化數(shù)據(jù)采集系統(tǒng)的設(shè)計(jì)方案,涵蓋系統(tǒng)架構(gòu)、關(guān)鍵技術(shù)與實(shí)現(xiàn)路徑。

一、 系統(tǒng)總體架構(gòu)設(shè)計(jì)

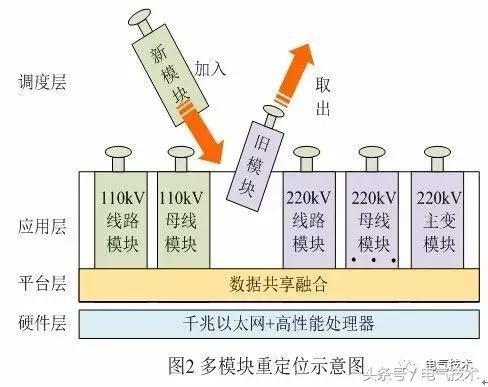

本系統(tǒng)采用模塊化、分層化的設(shè)計(jì)思想,總體架構(gòu)可分為四層:

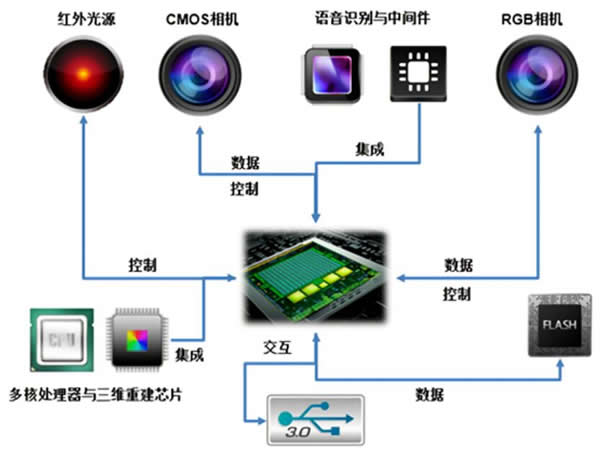

- 傳感與信號(hào)調(diào)理層:位于系統(tǒng)最前端,由各類傳感器(如射頻傳感器、光傳感器、溫度/壓力傳感器等)及對(duì)應(yīng)的信號(hào)調(diào)理電路組成。其核心任務(wù)是完成物理信號(hào)的感知,并將其轉(zhuǎn)換為適合后續(xù)處理的電信號(hào)。為實(shí)現(xiàn)高速與高精度,本層需采用寬帶、低噪聲的傳感器和高速、高精度的運(yùn)放及濾波電路。

- 高速數(shù)據(jù)采集與轉(zhuǎn)換層:這是系統(tǒng)的核心。主要包括:

- 高速模數(shù)轉(zhuǎn)換器(ADC):選用采樣率在GSPS(每秒千兆次采樣)級(jí)別、分辨率在12位以上的高性能ADC,以滿足通信信號(hào)寬帶采集的需求。

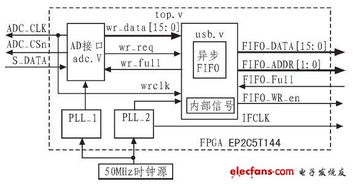

- 現(xiàn)場(chǎng)可編程門陣列(FPGA):作為采集控制與數(shù)據(jù)預(yù)處理的核心。FPGA負(fù)責(zé)產(chǎn)生精確的采樣時(shí)鐘,控制ADC的采樣時(shí)序,并對(duì)ADC輸出的高速原始數(shù)據(jù)進(jìn)行實(shí)時(shí)預(yù)處理,如數(shù)字下變頻(DDC)、濾波、抽取等,以減輕后端處理壓力。

- 高速時(shí)鐘與同步電路:提供低抖動(dòng)、高穩(wěn)定性的時(shí)鐘源,并確保多通道采集間的嚴(yán)格同步,這對(duì)于相控陣、MIMO等通信應(yīng)用至關(guān)重要。

- 數(shù)據(jù)處理與傳輸層:主要負(fù)責(zé)數(shù)據(jù)的緩存、封裝和高速傳輸。FPGA預(yù)處理后的數(shù)據(jù)通過高速串行接口(如PCIe Gen3/4、JESD204B/C、或10G/40G以太網(wǎng))傳輸至主處理器(如高性能CPU或嵌入式處理器)。該層設(shè)計(jì)需確保數(shù)據(jù)傳輸?shù)膶?shí)時(shí)性與無阻塞,避免數(shù)據(jù)丟失。

- 控制、存儲(chǔ)與上層應(yīng)用層:由主處理器、大容量存儲(chǔ)設(shè)備(如SSD陣列)及上位機(jī)軟件構(gòu)成。主處理器運(yùn)行嵌入式Linux或?qū)崟r(shí)操作系統(tǒng),負(fù)責(zé)系統(tǒng)的整體調(diào)度、配置管理、數(shù)據(jù)的高級(jí)處理(如頻譜分析、協(xié)議解析)以及將數(shù)據(jù)存儲(chǔ)到本地或通過網(wǎng)絡(luò)上傳至云端。上位機(jī)軟件提供人機(jī)交互界面,用于系統(tǒng)監(jiān)控、參數(shù)設(shè)置和數(shù)據(jù)分析可視化。

二、 實(shí)現(xiàn)高速化的關(guān)鍵技術(shù)

- 高速ADC與JESD204B接口技術(shù):采用支持JESD204B/C標(biāo)準(zhǔn)的高速ADC。該標(biāo)準(zhǔn)利用高速串行鏈路替代傳統(tǒng)的并行LVDS接口,極大簡(jiǎn)化了PCB布局布線,提高了通道密度和抗干擾能力,是實(shí)現(xiàn)多通道、超高采樣率采集的關(guān)鍵。

- 基于FPGA的實(shí)時(shí)信號(hào)處理:利用FPGA的并行處理能力和可編程性,在數(shù)據(jù)流進(jìn)入CPU之前完成大量固定算法的預(yù)處理。例如,在軟件無線電(SDR)應(yīng)用中,直接在FPGA內(nèi)完成數(shù)字混頻、濾波和重采樣,僅將有效帶寬內(nèi)的基帶數(shù)據(jù)送出,大幅降低了數(shù)據(jù)速率和對(duì)后端傳輸帶寬的壓力。

- 低抖動(dòng)時(shí)鐘設(shè)計(jì)與分發(fā):使用高性能的鎖相環(huán)(PLL)和壓控晶體振蕩器(VCXO)產(chǎn)生超低抖動(dòng)的系統(tǒng)主時(shí)鐘。通過專用時(shí)鐘緩沖器和扇出芯片,將清潔的時(shí)鐘信號(hào)分配到各個(gè)ADC和FPGA,確保采樣時(shí)間的精確性,這是保證高動(dòng)態(tài)范圍和無雜散動(dòng)態(tài)范圍(SFDR)的基礎(chǔ)。

- 高速數(shù)據(jù)傳輸總線:在板級(jí)互聯(lián)中,優(yōu)先采用PCIe Express總線,其高帶寬和低延遲特性非常適合作為FPGA與CPU之間的數(shù)據(jù)通道。對(duì)于遠(yuǎn)程或分布式采集,則采用基于TCP/IP或定制UDP協(xié)議的高速以太網(wǎng)技術(shù)。

三、 實(shí)現(xiàn)集成化的設(shè)計(jì)策略

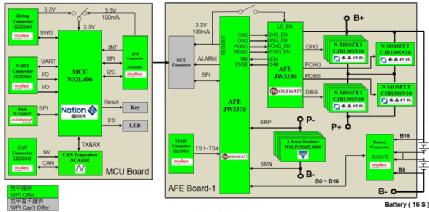

- 硬件集成:采用高密度、多層PCB設(shè)計(jì),將模擬前端、高速數(shù)字電路、電源管理模塊高度集成于一塊板卡上。使用集成度更高的芯片(如集成ADC、時(shí)鐘和數(shù)字處理的SoC FPGA),進(jìn)一步縮小體積,降低功耗。對(duì)于多通道系統(tǒng),可采用標(biāo)準(zhǔn)化的模塊(如FMC子卡)進(jìn)行擴(kuò)展,實(shí)現(xiàn)靈活配置。

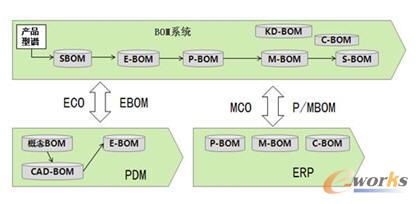

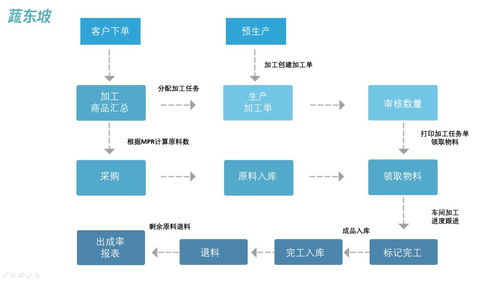

- 軟件集成:構(gòu)建統(tǒng)一的軟件框架。底層驅(qū)動(dòng)統(tǒng)一抽象為標(biāo)準(zhǔn)的API接口(如Linux IIO框架)。上層應(yīng)用軟件采用模塊化設(shè)計(jì),通過配置文件動(dòng)態(tài)加載不同的信號(hào)處理算法插件和數(shù)據(jù)存儲(chǔ)/上傳模塊,使系統(tǒng)能夠靈活適配不同的通信測(cè)試、監(jiān)測(cè)或控制系統(tǒng)。

- 智能與自適應(yīng)集成:在系統(tǒng)中集成微處理器或利用FPGA的軟核處理器,實(shí)現(xiàn)本地智能管理。系統(tǒng)能夠根據(jù)預(yù)設(shè)規(guī)則或?qū)崟r(shí)分析結(jié)果,自適應(yīng)調(diào)整采集參數(shù)(如采樣率、增益、中心頻率),實(shí)現(xiàn)從“固定采集”到“智能感知與采集”的演進(jìn)。

四、 系統(tǒng)性能評(píng)估與應(yīng)用展望

設(shè)計(jì)完成的系統(tǒng)需從采樣率、模擬帶寬、信噪比(SNR)、無雜散動(dòng)態(tài)范圍(SFDR)、通道間隔離度、數(shù)據(jù)傳輸延遲與穩(wěn)定性等多個(gè)維度進(jìn)行嚴(yán)格測(cè)試。

在通信工程中,此類高速集成數(shù)據(jù)采集系統(tǒng)具有廣闊的應(yīng)用前景:

- 5G/6G基站與終端測(cè)試:用于寬帶信號(hào)的發(fā)射與接收性能驗(yàn)證。

- 頻譜監(jiān)測(cè)與感知:實(shí)現(xiàn)大帶寬范圍內(nèi)的實(shí)時(shí)頻譜掃描與信號(hào)分析。

- 軟件無線電平臺(tái):作為通用硬件平臺(tái),通過加載不同軟件定義通信協(xié)議。

- 相控陣?yán)走_(dá)與衛(wèi)星通信:用于多通道射頻信號(hào)的高速同步采集與波束成形處理。

- 工業(yè)物聯(lián)網(wǎng)網(wǎng)關(guān):集成多種工業(yè)協(xié)議,高速采集現(xiàn)場(chǎng)設(shè)備數(shù)據(jù)并上傳。

結(jié)論

本文提出了一種面向現(xiàn)代通信工程的高速化與集成化數(shù)據(jù)采集系統(tǒng)設(shè)計(jì)方案。通過采用高速ADC、JESD204B接口、FPGA實(shí)時(shí)處理、低抖動(dòng)時(shí)鐘以及高速總線等關(guān)鍵技術(shù),并結(jié)合硬件、軟件與智能化的集成策略,該系統(tǒng)能夠有效滿足高速率、高精度、高可靠性的數(shù)據(jù)采集需求。該設(shè)計(jì)為通信設(shè)備的研發(fā)、測(cè)試、運(yùn)維以及新型通信技術(shù)的探索提供了強(qiáng)大的硬件基礎(chǔ),是推動(dòng)通信技術(shù)向更高帶寬、更低延遲、更廣連接發(fā)展的關(guān)鍵基礎(chǔ)設(shè)施之一。隨著芯片技術(shù)與標(biāo)準(zhǔn)協(xié)議的進(jìn)步,數(shù)據(jù)采集系統(tǒng)將向著更高采樣率、更寬帶寬、更強(qiáng)智能和更小體積的方向持續(xù)演進(jìn)。